What Is DO-254? A Complete Guide to Airborne Hardware Design Assurance

The Essential Guide to Requirements Management and Traceability

Chapters

- 1. Requirements Management

- Overview

- 1 What is Requirements Management? A Complete Guide

- 2 Why do you need Requirements Management?

- 3 Four Stages of Requirements Management Processes

- 4 Adopting an Agile Approach to Requirements Management

- 5 Status Request Changes

- 6 Conquering the 5 Biggest Challenges of Requirements Management

- 7 Three Reasons You Need a Requirements Management Solution

- 8 Guide to Poor Requirements: Identify Causes, Repercussions, and How to Fix Them

- 2. Writing Requirements

- Overview

- 1 Functional requirements examples and templates

- 2 Identifying and Measuring Requirements Quality

- 3 How to Write a System Requirements Specification (SRS) Document

- 4 The Fundamentals of Business Requirements: Examples of Business Requirements and the Importance of Excellence

- 5 Adopting the EARS Notation to Improve Requirements Engineering

- 6 Jama Connect Advisor™

- 7 Frequently Asked Questions about the EARS Notation and Jama Connect Advisor™

- 8 How to Write an Effective Product Requirements Document (PRD)

- 9 Functional vs. Non-Functional Requirements

- 10 What Are Nonfunctional Requirements and How Do They Impact Product Development?

- 11 Characteristics of Effective Software Requirements and Software Requirements Specifications (SRS)

- 12 What Is a Software Design Specification? Key Components + Template

- 13 8 Do’s and Don’ts for Writing Requirements

- 3. Requirements Gathering and Management Processes

- Overview

- 1 Requirements Engineering

- 2 Requirements Analysis

- 3 A Guide to Requirements Elicitation for Product Teams

- 4 Requirements Gathering Techniques for Agile Product Teams

- 5 Requirements Gathering in Software Engineering: Process, Techniques, and Best Practices

- 6 Defining and Implementing a Requirements Baseline

- 7 Managing Project Scope — Why It Matters and Best Practices

- 8 How Long Do Requirements Take?

- 9 How to Reuse Requirements Across Multiple Products

- 4. Requirements Traceability

- Overview

- 1 How is Traceability Achieved? A Practical Guide for Engineers

- 2 What is Requirements Traceability? Importance Explained

- 3 Tracing Your Way to Success: The Crucial Role of Traceability in Modern Product and Systems Development

- 4 Bidirectional Traceability: What It Is and How to Implement It

- 5 What is Engineering Change Management (ECM)? A Complete Guide

- 6 Change Impact Analysis (CIA): A Short Guide for Effective Implementation

- 7 What is Meant by Version Control?

- 8 What is Requirements Traceability and Why Does It Matter for Product Teams?

- 9 Key Traceability Challenges and Tips for Ensuring Accountability and Efficiency

- 10 The Role of a Data Thread in Product and Software Development

- 11 Unraveling the Digital Thread: Enhancing Connectivity and Efficiency

- 12 What is a Traceability Matrix? A Guide to Requirements Traceability

- 13 How to Create and Use a Requirements Traceability Matrix (RTM)

- 14 Traceability Matrix 101: Why It’s Not the Ultimate Solution for Managing Requirements

- 15 Live Traceability vs. After-the-Fact Traceability

- 16 Overcoming Barriers to Live Requirements Traceability™

- 17 Requirements Traceability, What Are You Missing?

- 18 Four Best Practices for Requirements Traceability

- 19 Requirements Traceability: Links in the Chain

- 20 What Are the Benefits of End-to-End Traceability During Product Development?

- 21 FAQs About Requirements Traceability

- 5. Requirements Management Tools and Software

- Overview

- 1 Selecting the Right Requirements Management Tools and Software

- 2 Why Investing in Requirements Management Software Makes Business Sense During an Economic Downturn

- 3 Why Word and Excel Alone is Not Enough for Product, Software, and Systems Development

- 4 Can You Track Requirements in Excel?

- 5 What Is Application Lifecycle Management (ALM)?

- 6 Is There Life After DOORS®?

- 7 Can You Track Requirements in Jira?

- 8 Checklist: Selecting a Requirements Management Tool

- 6. Requirements Validation and Verification

- 7. Meeting Regulatory Compliance and Industry Standards

- Overview

- 1 Understanding ISO Standards

- 2 Understanding ISO/IEC 27001: A Guide to Information Security Management

- 3 What is DevSecOps? A Guide to Building Secure Software

- 4 Compliance Management

- 5 What is FMEA? Failure Mode and Effects Analysis Guide

- 6 TÜV SÜD: Ensuring Safety, Quality, and Sustainability Worldwide

- 8. Systems Engineering

- Overview

- 1 What is Systems Engineering?

- 2 How Do Engineers Collaborate? A Guide to Streamlined Teamwork and Innovation

- 3 The Systems Engineering Body of Knowledge (SEBoK)

- 4 What is MBSE? Model-Based Systems Engineering Explained

- 5 Digital Engineering Between Government and Contractors

- 6 Digital Engineering Tools: The Key to Driving Innovation and Efficiency in Complex Systems

- 9. Automotive Development

- 10. Medical Device & Life Sciences Development

- Overview

- 1 The Importance of Benefit-Risk Analysis in Medical Device Development

- 2 Software as a Medical Device: Revolutionizing Healthcare

- 3 What’s a Design History File, and How Are DHFs Used by Product Teams?

- 4 Navigating the Risks of Software of Unknown Pedigree (SOUP) in the Medical Device & Life Sciences Industry

- 5 What is ISO 13485? Your Comprehensive Guide to Compliant Medical Device Manufacturing

- 6 What You Need to Know: ANSI/AAMI SW96:2023 — Medical Device Security

- 7 ISO 13485 vs ISO 9001: Understanding the Differences and Synergies

- 8 What Is IEC 62304? A Guide to Medical Device Software

- 9 Failure Modes, Effects, and Diagnostic Analysis (FMEDA) for Medical Devices: What You Need to Know

- 10 Embracing the Future of Healthcare: Exploring the Internet of Medical Things (IoMT)

- 11 What Is General Safety and Performance Requirements (GSPR)? What You Need To Know

- 11. Aerospace & Defense Development

- 12. Architecture, Engineering, and Construction (AEC industry) Development

- 13. Industrial Manufacturing & Machinery, Automation & Robotics, Consumer Electronics, and Energy

- 14. Semiconductor Development

- 15. AI in Product Development

- 16. Risk Management

- 17. Product Development Terms and Definitions

Chapter 11: What Is DO-254? A Complete Guide to Airborne Hardware Design Assurance

Chapters

- 1. Requirements Management

- Overview

- 1 What is Requirements Management? A Complete Guide

- 2 Why do you need Requirements Management?

- 3 Four Stages of Requirements Management Processes

- 4 Adopting an Agile Approach to Requirements Management

- 5 Status Request Changes

- 6 Conquering the 5 Biggest Challenges of Requirements Management

- 7 Three Reasons You Need a Requirements Management Solution

- 8 Guide to Poor Requirements: Identify Causes, Repercussions, and How to Fix Them

- 2. Writing Requirements

- Overview

- 1 Functional requirements examples and templates

- 2 Identifying and Measuring Requirements Quality

- 3 How to Write a System Requirements Specification (SRS) Document

- 4 The Fundamentals of Business Requirements: Examples of Business Requirements and the Importance of Excellence

- 5 Adopting the EARS Notation to Improve Requirements Engineering

- 6 Jama Connect Advisor™

- 7 Frequently Asked Questions about the EARS Notation and Jama Connect Advisor™

- 8 How to Write an Effective Product Requirements Document (PRD)

- 9 Functional vs. Non-Functional Requirements

- 10 What Are Nonfunctional Requirements and How Do They Impact Product Development?

- 11 Characteristics of Effective Software Requirements and Software Requirements Specifications (SRS)

- 12 What Is a Software Design Specification? Key Components + Template

- 13 8 Do’s and Don’ts for Writing Requirements

- 3. Requirements Gathering and Management Processes

- Overview

- 1 Requirements Engineering

- 2 Requirements Analysis

- 3 A Guide to Requirements Elicitation for Product Teams

- 4 Requirements Gathering Techniques for Agile Product Teams

- 5 Requirements Gathering in Software Engineering: Process, Techniques, and Best Practices

- 6 Defining and Implementing a Requirements Baseline

- 7 Managing Project Scope — Why It Matters and Best Practices

- 8 How Long Do Requirements Take?

- 9 How to Reuse Requirements Across Multiple Products

- 4. Requirements Traceability

- Overview

- 1 How is Traceability Achieved? A Practical Guide for Engineers

- 2 What is Requirements Traceability? Importance Explained

- 3 Tracing Your Way to Success: The Crucial Role of Traceability in Modern Product and Systems Development

- 4 Bidirectional Traceability: What It Is and How to Implement It

- 5 What is Engineering Change Management (ECM)? A Complete Guide

- 6 Change Impact Analysis (CIA): A Short Guide for Effective Implementation

- 7 What is Meant by Version Control?

- 8 What is Requirements Traceability and Why Does It Matter for Product Teams?

- 9 Key Traceability Challenges and Tips for Ensuring Accountability and Efficiency

- 10 The Role of a Data Thread in Product and Software Development

- 11 Unraveling the Digital Thread: Enhancing Connectivity and Efficiency

- 12 What is a Traceability Matrix? A Guide to Requirements Traceability

- 13 How to Create and Use a Requirements Traceability Matrix (RTM)

- 14 Traceability Matrix 101: Why It’s Not the Ultimate Solution for Managing Requirements

- 15 Live Traceability vs. After-the-Fact Traceability

- 16 Overcoming Barriers to Live Requirements Traceability™

- 17 Requirements Traceability, What Are You Missing?

- 18 Four Best Practices for Requirements Traceability

- 19 Requirements Traceability: Links in the Chain

- 20 What Are the Benefits of End-to-End Traceability During Product Development?

- 21 FAQs About Requirements Traceability

- 5. Requirements Management Tools and Software

- Overview

- 1 Selecting the Right Requirements Management Tools and Software

- 2 Why Investing in Requirements Management Software Makes Business Sense During an Economic Downturn

- 3 Why Word and Excel Alone is Not Enough for Product, Software, and Systems Development

- 4 Can You Track Requirements in Excel?

- 5 What Is Application Lifecycle Management (ALM)?

- 6 Is There Life After DOORS®?

- 7 Can You Track Requirements in Jira?

- 8 Checklist: Selecting a Requirements Management Tool

- 6. Requirements Validation and Verification

- 7. Meeting Regulatory Compliance and Industry Standards

- Overview

- 1 Understanding ISO Standards

- 2 Understanding ISO/IEC 27001: A Guide to Information Security Management

- 3 What is DevSecOps? A Guide to Building Secure Software

- 4 Compliance Management

- 5 What is FMEA? Failure Mode and Effects Analysis Guide

- 6 TÜV SÜD: Ensuring Safety, Quality, and Sustainability Worldwide

- 8. Systems Engineering

- Overview

- 1 What is Systems Engineering?

- 2 How Do Engineers Collaborate? A Guide to Streamlined Teamwork and Innovation

- 3 The Systems Engineering Body of Knowledge (SEBoK)

- 4 What is MBSE? Model-Based Systems Engineering Explained

- 5 Digital Engineering Between Government and Contractors

- 6 Digital Engineering Tools: The Key to Driving Innovation and Efficiency in Complex Systems

- 9. Automotive Development

- 10. Medical Device & Life Sciences Development

- Overview

- 1 The Importance of Benefit-Risk Analysis in Medical Device Development

- 2 Software as a Medical Device: Revolutionizing Healthcare

- 3 What’s a Design History File, and How Are DHFs Used by Product Teams?

- 4 Navigating the Risks of Software of Unknown Pedigree (SOUP) in the Medical Device & Life Sciences Industry

- 5 What is ISO 13485? Your Comprehensive Guide to Compliant Medical Device Manufacturing

- 6 What You Need to Know: ANSI/AAMI SW96:2023 — Medical Device Security

- 7 ISO 13485 vs ISO 9001: Understanding the Differences and Synergies

- 8 What Is IEC 62304? A Guide to Medical Device Software

- 9 Failure Modes, Effects, and Diagnostic Analysis (FMEDA) for Medical Devices: What You Need to Know

- 10 Embracing the Future of Healthcare: Exploring the Internet of Medical Things (IoMT)

- 11 What Is General Safety and Performance Requirements (GSPR)? What You Need To Know

- 11. Aerospace & Defense Development

- 12. Architecture, Engineering, and Construction (AEC industry) Development

- 13. Industrial Manufacturing & Machinery, Automation & Robotics, Consumer Electronics, and Energy

- 14. Semiconductor Development

- 15. AI in Product Development

- 16. Risk Management

- 17. Product Development Terms and Definitions

What Is DO-254? A Complete Guide to Airborne Hardware Design Assurance

Every chip inside an aircraft cockpit has to earn its place, and DO-254 is how hardware teams prove their designs are ready to fly. The standard gives you a clear process for demonstrating that your FPGAs, ASICs, and other complex devices meet the safety bar that certification authorities expect. Whether you are building your first airborne system or preparing for a certification review, understanding DO-254 is the starting point. This guide covers the standard’s scope, how Design Assurance Levels (DALs) work, the hardware development lifecycle, verification requirements, and common compliance challenges.

What Is DO-254?

DO-254 is the design assurance standard for airborne electronic hardware. It covers the chips, programmable devices, and custom circuits inside aircraft systems, and it tells hardware teams what development and verification processes they need to follow to get those components certified for flight. The standard doesn’t prescribe how to design hardware. It defines the process evidence that proves your design is safe enough to fly.

Both the FAA and EASA recognize DO-254 as an accepted means of compliance. The FAA’s AC 20-152A covers hardware at DAL A, B, and C, and EASA’s equivalent is AMC 20-152A.

Which Hardware Does DO-254 Cover (and Which Doesn’t)?

Simple hardware (discrete logic gates, basic analog circuits) can be verified exhaustively because every operating state is testable. Complex hardware like FPGAs, ASICs, and PLDs cannot, because programmable logic creates too many internal states for exhaustive testing. DO-254 exists specifically for that second category.

Surface-mounted resistors, capacitors, and individual electronic components are explicitly excluded. Circuit board assemblies fall within scope when they contain complex custom devices or complex commercial off-the-shelf (COTS) components.

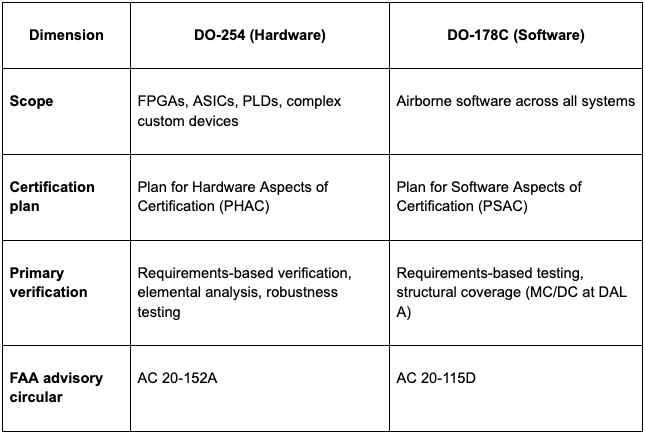

DO-254 vs. DO-178C: Hardware and Software Assurance Compared

Both standards use the same five-level DAL framework, but they govern different domains. DO-254 addresses airborne hardware, while DO-178C addresses airborne software.

The main difference is that DO-254 describes what needs to be done with limited guidance on how, while DO-178C is more prescriptive and includes technology supplements (DO-331, DO-332, DO-333) that DO-254 does not have. The tool qualification standard DO-330 applies to both. At the system level, ARP 4754A sits above both standards, flowing DALs down to hardware and software simultaneously.

Design Assurance Levels (DAL A Through E)

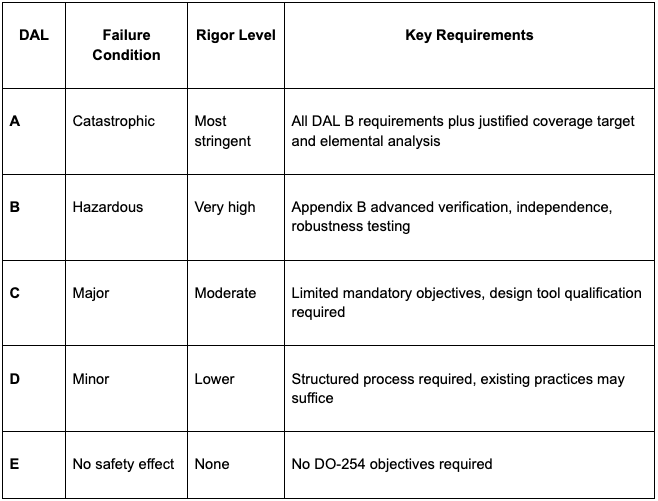

DALs classify how rigorous the development assurance process needs to be, based on the severity of the failure condition the hardware contributes to. DAL A requires the most stringent process objectives. Rigor decreases through each subsequent level until DAL E, which carries no DO-254 objectives at all.

How DALs Are Assigned

A Functional Hazard Assessment identifies potential failure conditions and classifies them by severity. The Preliminary System Safety Assessment then evaluates proposed architectures and allocates DALs to specific hardware items. A system function classified at the catastrophic level does not automatically assign DAL A to every hardware item implementing it. The system architecture can provide independent failure paths that allow a lower DAL for specific components.

What Each DAL Requires

Here is how the five DALs break down in terms of failure severity, rigor, and what the standard actually asks for at each level.

DAL A and B programs share many of the same advanced verification expectations, so teams often plan for both together.

Ready to Find Out More?

Our team of experts is here to answer any questions and learn how we can help enable your continued success. Get started with a free 30-day trial, or book a demo!

The DO-254 Hardware Development Lifecycle

DO-254 structures hardware development into sequential phases. Each phase produces specific lifecycle data that certification authorities review at defined milestones.

Planning the PHAC

The PHAC is the primary planning document you submit to the certification authority. It defines the processes, methods, standards, and lifecycle data that will satisfy DO-254 objectives. Alongside it, the planning phase produces the Hardware Development Plan, Verification and Validation Plan, Configuration Management Plan, and Process Assurance Plan. All of these are evaluated for completeness and consistency at the first Stage of Involvement (SOI #1).

Managing Configuration

Configuration management in DO-254 means maintaining controlled, auditable records of every piece of lifecycle data from the moment it is created: requirements, design files, HDL source, synthesis configurations, test procedures, results, and planning documents. It comes down to three things: version control so every change is recorded, baseline management so you can identify the exact state of all data at any milestone, and change tracking so every modification has a documented reason and approval.

Auditors focus heavily on CM because it ties the entire evidence base together. If a certification authority cannot trace a requirement change through design updates, re-verification, and updated results, the assurance argument breaks down. Teams that enforce CM from day one avoid the expensive rework that comes from treating it as a late-stage cleanup.

Defining Requirements, Design, and Implementation

The requirements phase produces documented, testable hardware requirements with unique identifiers. Each requirement is captured and traced before any Register Transfer Level (RTL) code is written, preventing verification gaps later in the lifecycle.

Conceptual design translates requirements into a high-level hardware architecture with partitioning strategies and interface definitions. Detailed design then produces implementation-ready data, including schematics, HDL code, netlists, and specifications. For FPGAs and ASICs, implementation means synthesis, place-and-route, and bitstream generation. For board-level hardware, it means PCB layout and fabrication.

Completing Stages of Involvement (SOI Reviews)

DO-254 programs follow four SOI milestones as formal review points with the certification authority:

- SOI #1 (Planning Review): Plans and standards are complete.

- SOI #2 (Design Review): Requirements and design data are assessed.

- SOI #3 (Verification Review): Verification evidence is reviewed.

- SOI #4 (Final Review): The completed Hardware Accomplishment Summary and full lifecycle data package are ready following the final hardware build.

Unresolved action items from earlier SOI reviews create gaps in the verification evidence base that are expensive to close later.

Key DO-254 Deliverables

DO-254 programs produce a specific set of lifecycle documents reviewed at SOI milestones. The exact content scales with DAL, but the core deliverables include the following:

- PHAC (Plan for Hardware Aspects of Certification): Defines the overall certification strategy, including processes, standards, and lifecycle data to be produced.

- HDP (Hardware Development Plan): Describes the development process, team roles, design methods, and tools used throughout the lifecycle.

- HVVP (Hardware Verification and Validation Plan): Specifies verification methods, test strategies, coverage targets, and pass/fail criteria for each lifecycle phase.

- HPAP (Hardware Process Assurance Plan): Establishes how process compliance will be monitored and how deviations will be handled.

- HCMP (Hardware Configuration Management Plan): Defines version control, baseline management, and change tracking procedures for all lifecycle data.

- HRD (Hardware Requirements Data): The documented set of hardware requirements, each with a unique identifier and traceability to system-level requirements.

- HDS (Hardware Design Data): Captures the conceptual and detailed design, including architecture descriptions, schematics, HDL code, and interface definitions.

- HAS (Hardware Accomplishment Summary): A final summary document that records what was planned, what was actually done, any deviations, and open problem reports. This is the last document reviewed at SOI #4.

Together, these deliverables form the evidence base that certification authorities evaluate across all four SOI milestones.

Verification and Validation Under DO-254

DO-254 treats verification and validation as a supporting process that runs throughout the development lifecycle, not as a single post-design phase. Validation determines that requirements are correct and complete, while verification evaluates whether an implementation meets those stated requirements. Confusing them can lead to evidence gaps that auditors will flag during SOI reviews.

Verification Methods and Requirements-Based Testing

Three verification methods must be combined to satisfy DO-254 objectives:

- Reviews: Applied throughout the lifecycle to assess requirements, design data, test plans, and test results.

- Analysis: Includes simulation, static timing analysis, formal analysis, and structural coverage measurement.

- Testing: Performed at both simulation and on-target hardware levels. DAL A and B programs commonly require pin-level verification through both.

Teams combine these methods to build complete requirements-based verification evidence. Traceability between requirements and verification artifacts is required, and independent reviews are mandatory for DAL A and B hardware.

For DAL A and B, the standard also requires elemental analysis: systematically examining each design element (HDL modules, logic blocks, functional partitions) to confirm verification has exercised it. Teams map every element to the test cases and analysis results that cover it, then review for gaps. DAL A requires a justified coverage target; DAL B has slightly less prescriptive expectations. This is one of the most labor-intensive activities in a DO-254 program, and where incomplete traceability becomes most visible.

Tool qualification under DO-330 is also part of the verification picture. Qualification rigor depends on the tool type, its intended use, and the potential impact of tool errors on the hardware.

Building a Requirements Traceability Matrix

Traceability is a core structural requirement in DO-254. Downstream traceability reveals requirements that lack verification coverage, while upstream traceability surfaces derived requirements and unused HDL functions. For DAL A and B, full bidirectional traceability through requirements, design, implementation, and verification results is required. For DAL C and D, traceability from requirements to test is sufficient.

Compliance Challenges and How to Reduce Certification Risk

The most expensive DO-254 problems start with inadequate planning. Teams that build traceability retroactively before an audit face high rework costs, and treating configuration management as an end-of-process activity makes it harder for auditors to reconstruct development history. DAL A and B devices require independent verification, so the designer cannot perform verification for certification credit, which directly affects team structure and scheduling.

The programs that control costs invest in early PHAC development, maintain continuous traceability and configuration management from day one, and engage certification authorities early to close interpretive gaps before building an evidence base on uncertain assumptions.

How Jama Connect Supports DO-254 Compliance

When traceability, test evidence, and change records live in disconnected spreadsheets, preparing for SOI reviews gets slower and more error-prone. Jama Connect® keeps hardware requirements, verification artifacts, and review evidence linked across the DO-254 lifecycle, so you’re not rebuilding trace data before each review. Live Traceability™ lets you compare required data traces against actual development activity and surface coverage gaps before an SOI milestone.

Getting Started With DO-254 Compliance

The programs that get through certification smoothly share a common thread: they invest in planning, traceability, and configuration management from day one rather than scrambling to assemble evidence before an audit. If you are ready to put that structure in place, start a free 30-day trial of Jama Connect and see how live traceability works across the DO-254 lifecycle.

Frequently Asked Questions About DO-254

Who is required to comply with DO-254?

If your program develops FPGAs, ASICs, PLDs, or other complex custom devices for civil airborne systems at DAL A, B, or C, DO-254 is the accepted means of compliance. This applies to manufacturers and installers pursuing type certification, TSO authorization, supplemental type certificates, and related approvals under FAA jurisdiction. EASA-jurisdiction programs follow equivalent requirements through AMC 20-152A.

What is the difference between DO-254 and DO-178C?

DO-254 covers hardware, DO-178C covers software, and both use the same DAL framework. The main difference for teams is that DO-178C is more prescriptive and includes technology supplements that DO-254 doesn’t have. On most avionics programs, hardware and software teams work to both standards in parallel under ARP 4754A system-level guidance.

What role does requirements traceability play in DO-254 compliance?

Traceability is one of the first things certification authorities check. For DAL A and B, you need full bidirectional traceability across requirements, design, implementation, and test results. Teams that build it into their workflow from day one spend far less time preparing for SOI reviews than teams that try to assemble it retroactively.

Does DO-254 apply to commercial off-the-shelf (COTS) components?

COTS components are addressed within current DO-254 compliance guidance. Specific objectives for COTS devices are separate from the objectives for custom programmable devices. COTS IP cores used within FPGAs or ASICs are also addressed through separate IP objectives.

Watch our webinar on the Space Systems Framework in Jama Connect®

DO-254 is the design assurance standard for airborne electronic hardware.

Book a Demo

See Jama Connect in Action!

Our Jama Connect experts are ready to guide you through a personalized demo, answer your questions, and show you how Jama Connect can help you identify risks, improve cross-team collaboration, and drive faster time to market.